TSMC fa il punto sui processi produttivi: accelerazione verso i 4 nanometri

La taiwanese TSMC è sotto pressione in questi mesi per la grandissima richiesta di microchip che interessa praticamente ogni settore industriale e che arriva da clienti come Apple, MediaTek, Qualcomm, Nvidia, AMD solo per citarne alcuni. Il produttore ha promesso ingenti investimenti per migliorare la sua capacità produttiva, ma come ormai ben chiaro a tutti serviranno molti mesi, se non uno-due anni per uscire completamente dalla situazione di shortage che sta limitando la disponibilità di prodotti tecnologici e frenando settori come quello dell’auto, sempre più dipendente dai chip.

Ciononostante, lo sviluppo dei processi produttivi va avanti, e TSMC ne ha parlato durante il suo recente Technology Symposium, dove ha fatto il punto su quelle tecnologie avanzate che permetteranno ai suoi clienti di progettare e portare sul mercato chip sempre più evoluti.

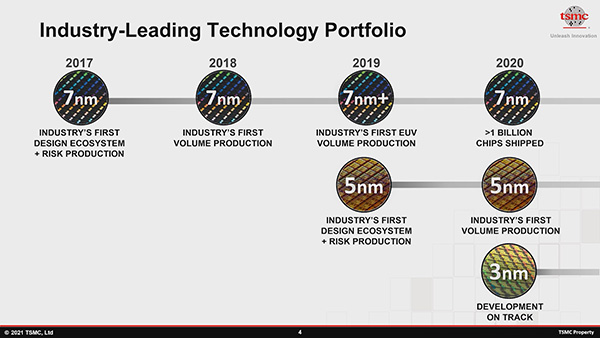

Il processo produttivo a 7 nanometri (N7), ad esempio, la cui produzione in volumi è iniziata nel 2018, continua a essere un punto fermo dell’industria, tanto che finora sono stati consegnati oltre 1 miliardo di chip realizzati con tale processo. L’azienda taiwanese, i cui clienti stanno volgendo lo sguardo al prossimo step – i 5 nanometri (N5) -, prevede per l’anno in corso un aumento della capacità produttiva a 7 nanometri solo del 14%, un rallentamento fisiologico rispetto agli anni passati.

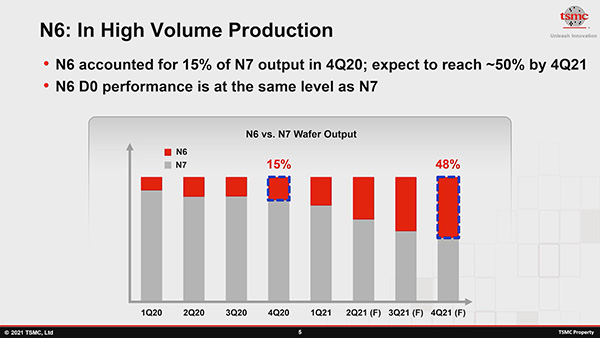

Un altro processo produttivo sempre più importante è quello a 6 nanometri (N6). Essendo un processo in continuità con quello N7, molti clienti lo stanno adottando con un ritmo impressionante: secondo TSMC, il volume produttivo del processo N6 passerà dal 15% del Q4 2020 al 48% nell’ultimo trimestre di quest’anno se rapportato ai 7 nanometri.

L’azienda taiwanese non ha indicato quali sono i clienti dei 6 nanometri, ma sappiamo per certo che Qualcomm e MediaTek sono sicuramente della partita con alcuni SoC mobile. Non è poi da escludere per il quarto trimestre l’adozione della tecnologia da parte di qualche azienda del settore PC e HPC, anche se al momento non ci sono conferme in merito.

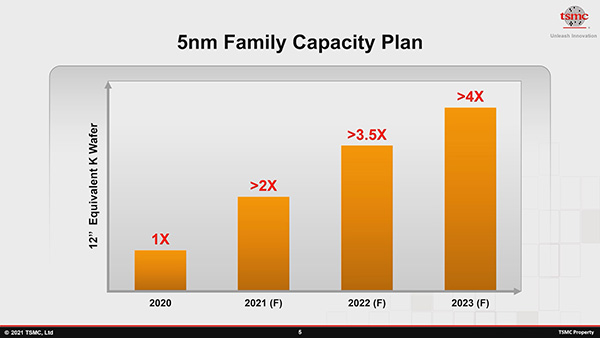

I 5 nanometri sono in produzione in volumi dall’anno passato, con Apple che lo sta usando per la realizzazione dei SoC A14 degli iPhone e il chip M1 dei nuovi Mac e non solo. Finora TSMC ha consegnato 500 mila wafer a 5 nanometri, producendo verosimilmente alcune centinaia di milioni di chip.

Nel 2020 la casa di Cupertino ha sicuramente giocato la parte del leone negli ordini di chip a 5 nanometri, ma TSMC prevede di raddoppiare i wafer prodotti quest’anno e di quadruplicare il dato del 2020 entro il 2023. In termini di rese, i 5 nanometri hanno raggiunto risultati migliori rispetto ai 7 nanometri, soprattutto grazie all’uso della litografia EUV che semplifica alcuni passaggi.

In concomitanza con il Technology Symposium, TSMC ha introdotto una nuova variante dei 5 nanometri chiamata N5A, destinata a “soddisfare la crescente domanda di potenza di calcolo in nuove e più intensive applicazioni automotive come l’assistenza alla guida gestita dall’intelligenza artificiale e la digitalizzazione dei cruscotti sui veicoli”. N5A nasce quindi per garantire le prestazioni, l’efficienza energetica e la densità logica del processo N5 rispettando alcuni requisiti di affidabilità richiesti dal settore dell’auto: sarà a disposizione dei clienti dal terzo trimestre 2022.

L’azienda ha inoltre parlato del processo N4, ossia i suoi 4 nanometri, annunciati lo scorso giugno come evoluzione dei 5 nanometri. Il processo promette una densità del 6% superiore ai 5 nanometri e una minore complessità grazie all’uso di un minor numero di maschere. Si prevedono le stesse rese dei 5 nanometri e lo sviluppo procede spedito verso la fase di “risk production” nel corso del terzo trimestre, prima di quanto si pensava inizialmente (Q4).

TSMC ha parlato dei 3 nanometri (N3) che entreranno nella fase di produzione in volumi nella seconda metà del 2022. A differenza di altre soluzioni, come quella adottata da IBM per il suo processo a 2 nanometri, l’azienda taiwanese continuerà ad affidarsi all’architettura dei transistor FinFET per garantire fino al 15% di prestazioni in più o un consumo del 30% in meno rispetto ai 5 nanometri (N5), garantendo al tempo stesso un aumento della densità logica del 70%.

Infine, sappiamo da tempo che l’azienda sta lavorando anche sul processo a 2 nanometri (N2) e probabilmente al passaggio ai transistor gate-all-around (GAAFET): siamo ancora alla fase di ricerca in questo momento, il che significa che è semplicemente troppo presto per parlarne.

Fonte: http://feeds.hwupgrade.it/