Xeon Clearwater Forest, oltre il processo Intel 18A c’è di più

Nei giorni scorsi sono emersi interessanti dettagli tecnici su Clearwater Forest, nome in codice di un processore Xeon di Intel previsto per il 2025 e interamente basato su E-core. Fondamentalmente, il successore dello Xeon “Sierra Forest” che vedremo debuttare quest’anno.

Intel aveva già reso noto che i core (architettura Darkmont) saranno prodotti con processo Intel 18A, evoluzione di quello 20A che introdurrà, per la prima volta, i nuovi transistor RibbonFET e l’alimentazione dal retro dei transistor PowerVia.

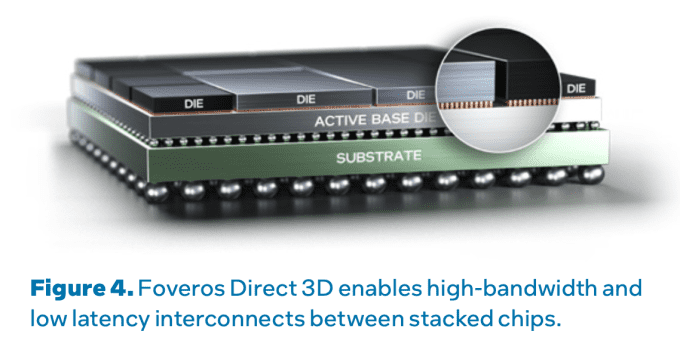

Questa però è solo una delle innovazioni del progetto Clearwater Forest, perché vedremo per la prima volta un package avanzato basato su due tecnologie chiamate Foveros Direct 3D e EMIB 3.5D. La prima consente ai chiplet impilati di essere collegati verticalmente in modo molto ravvicinato e consentire una bandwidth elevata.

Foveros Direct 3D si basa sul cosiddetto “hybrid bonding” tra i punti di contatto di ciascun chip. Le interconnessioni elettriche verticali in rame vengono allineate tra loro, operazione che Intel descrive come “collegamento a termocompressione dei collegamenti verticali in rame”. Qualcosa di simile alla tecnologia SoIC di TSMC che viene usata da AMD per la 3D V-Cache sulle CPU Ryzen.

Secondo Intel, Foveros Direct 3D può essere usato sia “face to face” che “face to back”. È anche possibile utilizzare wafer e chip di diversi produttori. La prima generazione di Foveros Direct 3D consentirà distanze tra i punti di saldatura (bump) di 9 µm. La generazione successiva scenderà a 3 µm.

Per la connessione tramite Foveros Direct 3D, Intel produrrà il die base di Clearwater Forest con processo Intel 3-T, una delle nuove tecnologie annunciate all’IFS Direct Connect. Nel suo documento, Intel parla della presenza di una cache locale nel die di base, che si aggiungerà a quella presente nella Compute Tile. Non è la prima volta che Intel integra una cache nella Base Tile, l’ha già fatto con l’acceleratore HPC Ponte Vecchio.

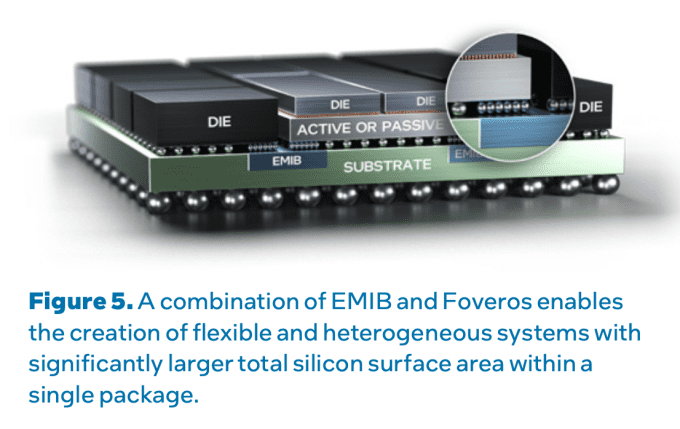

Per quanto riguarda EMIB 3.5D, si tratta della combinazione di EMIB e Foveros, ma le due tecnologie rappresentano due fasi e tecniche di processo separate. La seconda generazione di EMIB ridurrà il bump pitch da 55 a 45 µm.

Durante IFS Direct Connect 2024 l’amministratore delegato Pat Gelsinger ha mostrato un chip preliminare di Clearwater Forest, con le due Compute Tile al centro e due I/O Tile ai lati, in modo simile ai progetti Sierra Forest e Granite Rapids al debutto quest’anno.

Fonte: http://feeds.hwupgrade.it/