Transistor, è record: realizzato un gate di 0,34 nanometri, spesso quanto un singolo atomo

Lo schema base di un transistor ad effetto di campo prevede due elettrodi, chiamati source e drain, separati da un elemento semiconduttore, il gate. La dimensione del gate è una delle caratteristiche più importanti di un transistor, poiché da essa dipendono le dimensioni complessive del transistor (e quindi una possibilità di accedere a densità maggiori quando v’è da accorpare più transistor in un chip) e la velocità di switching (cioè la velocità di accensione/spegnimento del transistor): entrambi i parametri concorrono ad un incremento della capacità di calolo. Pertanto quando si parla di miniaturizzazione, in riferimento ai transistor e poi più in generale ai processori, si parla nella sostanza di questo: ridurre il più possibile la dimensione del gate.

Sappiamo che il silicio rappresenta il materiale semiconduttore d’elezione per questo tipo di applicazioni, anche se tuttavia i passi avanti nella direzione della miniaturizzazione dei transistor hanno subito un rallentamento nel corso degli ultimi anni, proprio per via dell’avvicinamento ad una serie di limiti fisici che non è possibile superare, che hanno imposto lo studio e l’impiego di nuovi materiali.

Una recente pubblicazione su Nature, ad opera di un gruppo di scienziati della School of Integrated Circuits presso la Tsinghua University di Beijing, in Cina, descrive una particolare tecnica che, grazie all’impiego del grafene, ha consentito di realizzare un transistor con un gate dello spessore di appena un atomo. Non solo: i ricercatori assicurano che grazie alla scelta di alcuni specifici materiali, e ad una particolare disposizione degli elementi, è possibile realizzare i transistor in maniera agevole e con dimensioni complessive compatte. Attualmente si tratta del più piccolo spessore di gate mai citato in una pubblicazione scientifica.

Il dispositivo più piccolo realizzato, sempre in un contesto sperimentale, in precedenza era caratterizzato da un gate costituito da un singolo nanotubo di carbonio, per uno spessore di appena 1 nanometro. I ricercatori hanno avuto l’intuizione di sfruttare il bordo di uno strato di grafene, che ricordiamo essere un foglio di carbonio dello spessore di un atomo, come gate del loro transistor.

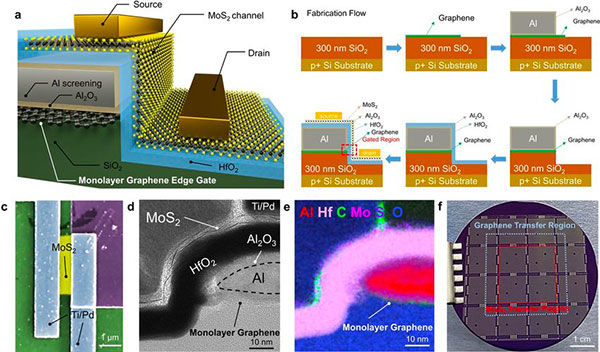

Per fare ciò sono stati usati degli strati di silicio (qui con funzione puramente strutturale, in quanto non è presente silicio nel transistor stesso) e biossido di silicio, sopra ai quali è stato stratificato un foglio di grafene per creare il materiale del gate. Al di sopra è stato deposto un ulteriore strato di ossido di alluminio. I ricercatori hanno quindi ottenuto una struttura in cui il foglio di grafene si è trovato interposto tra due ossidi isolanti.

Affinché il bordo del foglio di grafene potesse essere esposto in maniera utile, i ricercatori hanno praticato un’incisione lungo il bordo della struttura, fino al diossido di silicio sottostante, di fatto tagliando il foglio di grafene ed esponendo il bordo così da poterlo utilizzare come gate. Lo spessore del foglio è, come già indicato, di un atomo di carbonio ovvero 0,34 nanometri.

A questo punto sull’intera struttura, tridimensionale, è stato stratificato prima ossido di hafnio e poi del disolfuro di molibdeno, un materiale semiconduttore, in modo tale che il bordo del grafene si trovasse in stretta prossimità con esso, separato semplicemente dall’ossido di hafnio. In questo modo il bordo del grafene può agire da gate per controllare la conduttività del semiconduttore. Il passo successivo è stato quello di posizionare i due elettrodi, source e drain, sui due lati del gate, operazione facilitata dalla tridimensionalità della struttura. L’ulteriore aspetto chiave di questa tecnica è che non è richiesto un posizionamento estremamente preciso degli elettrodi.

Per verificare le proprietà del dispositivo i ricercatori hanno fatto largo uso di modellazione tridimensionale computerizzata, ma è stato comunque necessario procedere anche alla costruzione concreta di transistor con questa tecnica e configurazione. Una parte di questi sono stati impiegati per ottenere conferma visiva, tramite tecniche di imaging, della corretta collocazione dei materiali, mentre una parte è stata usata sperimentalmente per verificare il funzionamento del dispositivo.

Si tratta ovviamente di una ricerca ancora in fase embrionale, ma che ha almeno dimostrato la fattibilità e il funzionamento di transistor con gate estremamente ridotti impiegando una tecnica non particolarmente complessa. Ovviamente la strada è ancora parecchio lunga perché si possa anche solo lontanamente iniziare a parlare di adeguatezza commerciale, ma almeno un primo passo è stato compiuto.

Fonte: http://feeds.hwupgrade.it/